-

振东集团的”本草革命”:让中药材跳出药罐子,闯出大健康新天地

发布时间:2025/06/10

红球纷飞传三晋,大爱无边漫九州。5月25日,由中国红十字会总会主办,山西振东健康产业集团赞助的“红气球挑战赛”(晋中站)在山西省高校新区(山西大学城)鸣笛开赛。该赛事汇聚了来自全国各地及山西大学城高校的...

-

2025中美领衔世界级艺术名家 ——赵玉林精品展播

发布时间:2025/01/17

赵玉林,笔名三友,内蒙古包头市美术家协会副主席,草原书画院院长,中国美协内蒙古分会会员,台北故宫书画院名誉院长,中华国礼书画家,国家博物馆画廊特邀书画家。作品入选《中国当代国际书画家年鉴》,在中国书画研究...

-

腾讯创作者生态的前车之鉴,能否支撑《元梦之星》逐梦UGC?

发布时间:2023/09/24

近期,腾讯以“天美乐园”的特别形式公布了新作《元梦之星》,宣告正式入主派对游戏赛道。过去,派对游戏在国内市场份额较小,直到《糖豆人》《香肠派对》《蛋仔派对》等作品引发用户和市场的高度关注,整个赛道才...

-

普悦智能,专注净水,为渠道经销搭载新引擎!

发布时间:2023/08/28

稳步推进:祝贺普悦智能(北京联营公司)第一轮股东入股签约圆满成功! 2023年8月18日,浙江普悦智能科技有限公司北京联营公司——北京普悦京允智能科技有限公司在总经理宋玉财的热忱推进下,成功签约了五名销售/服...

-

英国与快速反应小组一起抗击冠状病毒

发布时间:2020/04/01

英国政府宣布了新的措施,以打击虚假的COVID-19在线信息的传播,包括建立专门的专家小组来处理错误信息。 新成立的快速反应小组将在英国内阁办公室内部运作,并将研究应对互联网上“有害叙述”的方法-解决“...

-

微软即将吸引消费者-但Skype仍将保留

发布时间:2020/03/31

微软今天宣布,今年晚些时候,它将推出Teams的基本消费版,即类似于Slack的文本,音频和视频聊天应用程序。就像Microsoft所喜欢的,您的个人生活团队将使用许多工具,这些工具将使家庭和小组更轻松地组织...

-

安全漏洞暴露了共和党选民公司的内部应用代码

发布时间:2020/03/31

一家专供共和党政治运动使用的选民联系和拉票公司,错误地在其网站上留下了未经保护的应用程序代码副本,供任何人找到。 Campaign Sidekick公司通过iOS和Android应用程序帮助共和党竞选活动布署其选区,这...

-

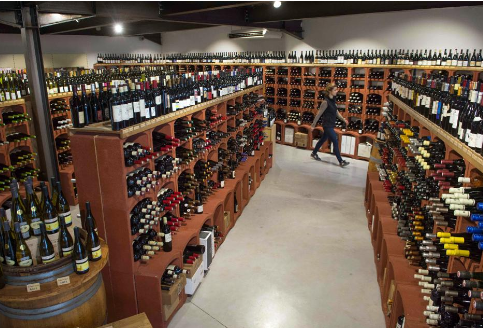

在宾夕法尼亚州,州酒商店仍然关闭,人们越来越口渴

发布时间:2020/03/31

随着美国人渴望长时间的自我隔离,白酒业务的销量激增。根据尼尔森(Nielsen)的数据,到3月中旬,这一增长已经比去年同期高出26%以上。但是,联盟中至少有一个州与这种趋势背道而驰,而且与消费者的意愿无...

推动未来发展:最小的全数字电路为5 nm下一代半导体打开大门

发布时间:2020/02/12 新闻 浏览次数:845

东京工业大学(Tokyo Tech)和Socionext Inc.的科学家设计了世界上最小的全数字锁相环(PLL)。 PLL实际上是所有数字应用中的关键时钟电路,而减小其尺寸并提高其性能是实现下一代技术发展的必要步骤。

人工智能,5G蜂窝通信和物联网等新技术或改进技术有望带来社会的革命性变化。但是要做到这一点,高性能的片上系统(SoC)(一种集成电路)设备是必不可少的。 SoC设备的核心组成部分是锁相环(PLL),该电路与参考振荡的频率同步并输出相同或更高频率的信号。 PLL产生“时钟信号”,其振荡充当节拍器,为数字设备的和谐运行提供精确的时序参考。

为了实现高性能SoC器件,半导体电子产品的制造工艺必须变得更加复杂。实现数字电路的面积越小,设备的性能越好。制造商一直在竞相开发越来越小的半导体。 7 nm半导体(比其10 nm的前代产品有了重大改进)已经投入生产,并且正在研究制造5 nm半导体的方法。

然而,在这一努力中存在主要瓶颈。现有的PLL需要模拟组件,这些组件通常体积庞大并且设计难以按比例缩小。

冈田贤一教授领导的东京理工大学和Socionext Inc.的科学家通过实现“可合成的”分数N PLL来解决此问题,该分数N PLL仅需要数字逻辑门,而无需笨重的模拟组件,因此易于采用传统的小型集成电路。

Okada及其团队使用了多种技术来降低其可合成PLL的所需面积,功耗和抖动(传输数字信号时的不必要的时间波动)。为了减小面积,他们采用了环形振荡器,这是一种易于缩小的紧凑型振荡器。为了抑制抖动,他们使用“注入锁定”来降低此环形振荡器的相位噪声(信号中的随机波动),该过程是使振荡器与频率接近(或多个)频率的外部信号同步的过程。振荡器—在很宽的频率范围内。较低的相位噪声又降低了功耗。

在许多重要方面,该可合成PLL的设计优于所有其他当前的最新PLL。它以最低的功耗和最小的面积实现了最佳的抖动性能(如图1所示)。 Okada表示:“核心面积为0.0036 mm2,整个PLL被实现为一种具有单个电源的布局。”此外,它可以使用标准的数字设计工具进行构建,从而实现快速,省力和低成本的生产,使其在商业上可行。

这种可合成的PLL可以轻松地集成到全数字SoC的设计中,并且具有商业可行性,使其对于开发5nm半导体的前沿应用(包括人工智能,物联网和许多其他应用)非常有价值。高性能和低功耗将是关键要求。但是这项研究的贡献超出了这些可能性。 “我们的工作证明了可合成电路的潜力。利用此处采用的设计方法,还可以使SoC的其他构建模块,例如数据转换器,电源管理电路和无线收发器,也可以合成。这将大大提高设计效率并大大减少了设计工作。”冈田解释说。 Tokyo Tech和Socionext将在此领域继续合作,以推进电子设备的小型化,从而实现新一代技术。